I. 서 론

II. 제안한 후단부 시스템 설계

2.1 대역통과필터 블록

2.2 디지털 시간-이득 보상 블록

2.3 포락선 검출 블록

2.4 신호 선별 블록

2.5 로그압축 블록

2.6 디지털주사변환 블록(Digital Scan Conversion; DSC)

2.7 디스플레이 버퍼 블록

III. 후단부 시스템 성능 평가 결과 및 고찰

3.1 MATLAB을 사용한 후단부 시스템 검증

3.2 후단부 시스템 리소스 사용량 평가

3.3 후단부 시스템 실시간 영상 성능 평가

3.4 고찰

IV. 결 론

I. 서 론

21세기에 들어오면서 심혈관계 질환은 암과 함께 우리나라뿐만 아니라 세계적으로 주요 사망원인의 1, 2위를 다투고 있다. 죽상동맥경화증은 협심증, 심근경색증, 뇌졸중 등 치명적인 심혈관계 질병의 원인으로 진단 및 치료방법에 대한 많은 연구들이 이어져오고 있다. 일반적인 진단방법으로 혈관조영술이 널리 사용되고 있으나 인체 내에 주입하는 조영제의 부작용에 대한 우려와 함께 X선이 투사되는 면과 직각을 이루는 평면의 영상만을 획득할 수 있어 병변의 3차원적 구조를 알기 어려워 정확한 진단이 힘들다는 단점이 있다.[1,2] 조영제 사용에 따른 부작용, 2차원적 구조의 병변 영상에 따른 진단의 어려움 등의 단점들을 보완하기 위하여 병변의 3차원 구조를 판단할 수 있는 혈관내초음파영상(Intravascular Ultrasound, IVUS), 광간섭단층영상(Optical Coherence Tomography, OCT) 등과 같은 다양한 진단 방법들이 대두되고 있다.[3] 죽상동맥경화증에 대한 치료방법으로는 스텐트를 사용하여 협착된 관상동맥을 확장하는 경피적관상동맥개입술(Percutaneous Coronary Intervention, PCI)과 협착된 관상동맥 부위를 대체 혈관으로 연결하는 관상동맥우회술(Coronary Artery Bypass Graft, CABG) 등이 대표적인 내 ‧ 외과적 치료방법으로 알려져 있다.

혈관내초음파 영상 장치들은 1800 rpm 이상의 회전속도로 카테터를 회전시키면서 20 MHz ~ 45 MHz의 초음파 주파수를 사용하여 약 150 µm의 공간해상도를 가지면서 10 mm 내외의 영상을 제공한다.[4] 혈관내초음파는 이런 기본적인 성능 때문에 내과적 치료방법인 PCI 시술 과정에서는 스텐트 시술의 적정화(stent optimization)를 시각적으로 판단할 수 있고 시술 후에는 추적관찰에 이용되어 재협착의 기전을 진단하는데 많은 정보를 제공할 수 있어 유용하게 사용되는 진단방법으로 각광을 받고 있다.[5,6] 이러한 이유로 혈관내초음파 영상장치는 심혈관계 관련된 시술·수술방에서 필요한 진단 장치로 효용성이 높아지고 있다. 상용 혈관내초음파 영상 장치들은 카트형 구조로 일정 부분의 공간 점유율을 차지하고 있어 수술방에서 공간 사용 편의성을 위하여 포터블 형태 또는 수술용 침대 부착 형태로의 소형화된 시스템에 대한 요구들도 성능 개선 등과 함께 요구되고 있다.

이러한 요구 조건들을 만족하는 시스템 소형화에 관한 연구들이 진행되어 왔다. 선행 연구들에 의해 소개된 시스템들의 후단부는 하나의 FPGA (Field Programmable Gate Array)와 외부 메모리로 구성되는 구조를 가진다.[7] 중저가의 FPGA들의 내부 메모리 최대 용량은 약 10 M bits으로 신호처리와 영상처리를 수행함에 있어 FPGA의 내부 메모리만으로 구현이 어렵기 때문에 외부 메모리를 사용하는 구조를 가지게 된다. 예를 들어, 250 MSPS(Mega Samples Per Second)인 12-bit ADC 사용하여 10 mm의 침투 깊이를 영상화할 경우, 혈관내초음파 영상을 구성하는 주사선이 1,024 개이고 각 주사선은 3,250개의 샘플로 구성되어 있으면 모든 주사선의 데이터를 저장하려면 적어도 40 M bits(12 × 3250 × 1024)의 메모리가 필요하다. 수신된 초음파 신호의 저장 후 신호처리를 거쳐서 401 × 401 픽셀의 크기로 영상화를 할 경우, 디지털주사변환을 위한 메모리 용량은 적어도 1.3 M bits(401 × 401 × 8) 이상이 필요하게 된다. 뿐만 아니라, 높은 샘플링 주파수로 30 프레임(1800 rpm ÷ 60 s = 30 frame/s) 이상의 실시간 영상 구현을 위해서는 최대 32.6 µs(1 s ÷ 30 frame ÷ 1,024 = 32.6 µs) 이내에 하나의 주사선에 대한 디지털신호처리 및 디지털주사변환이 이루어져야 한다. 즉, 일반적인 초음파 영상의 신호처리 및 영상처리 구조로 실시간 혈관내초음파 영상을 구현할 수 있는 소형 후단부 시스템을 구현하기란 쉽지 않다.

본 논문에서는 실시간 혈관내초음파 영상을 구현할 수 있는 후단부 시스템을 저비용, 소형화, 경량화가 가능한 구조를 제안한다. 제안한 구조를 적용하여 신호처리, 영상처리 구조의 최적화, 단순화를 통하여 외부 메모리 없이 단일 FPGA를 사용하여 실시간 혈관내초음파 영상을 구현할 수 있는 후단부 시스템의 설계 및 성능 평가를 소개한다.

II. 제안한 후단부 시스템 설계

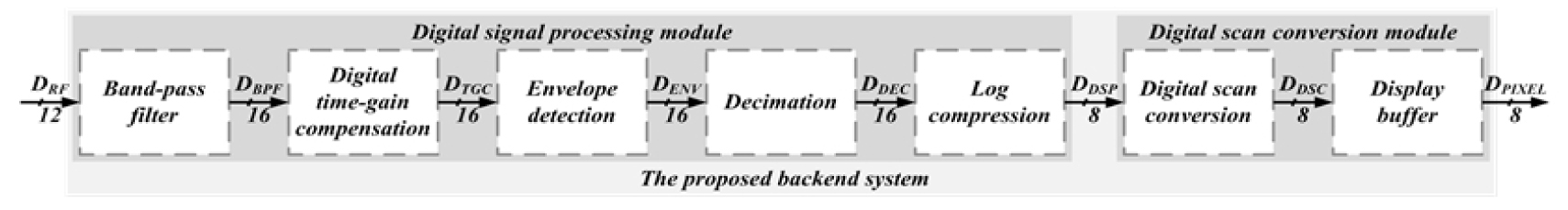

제안하는 후단부 시스템은 Fig. 1과 같이 디지털신호처리 모듈(Digital Signal Process, DSP), 디지털주사변환 모듈(Digital Scan Convert, DSC)의 두 개의 기능성 모듈로 구성된다. DSP 모듈은 ADC를 통하여 수신된 초음파 신호를 임상 정보를 가진 신호로 처리하는 기능을 하며 대역통과필터 블록, D-TGC 블록, 포락선 검출 블록, 신호 선별 블록, 로그압축 블록의 다섯 개의 세부 블록으로 구성되고 DSC 모듈은 DSP 모듈의 출력 데이터로부터 혈관내초음파 영상 형태의 영상 데이터로 변환하는 기능을 하며 DSC 블록과 디스플레이 버퍼 블록으로 구성된다. 실시간 영상을 위하여 연산처리시간이 긴 연산 과정들을 LUT (Look-up Table)의 형태로 바꾸어서 DSP 모듈의 연산처리시간을 단축하였고 외부 메모리 없이 단일 FPGA의 내부 메모리에 적용할 수 있도록 메모리 사용량을 줄일 수 있는 새로운 형태의 DSC 구조를 제안하여 구조를 단순화하였다. 기능성 모듈을 구성하는 일곱 개의 세부 블록은 다음과 같은 방법으로 설계하였다.

2.1 대역통과필터 블록

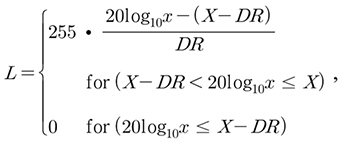

ADC로부터 수집된 수신신호에는 수신단의 전자소자에 의한 플리커 잡음이나 버스트 잡음이 포함될 수 있다. 이 잡음들은 DC 및 저주파수 대역의 큰 스펙트럼 요소를 가지므로 수신 신호를 왜곡하고 포락선 검출 시에 정확한 계산을 방해한다. 또한 넓은 대역폭을 가지는 초음파 변환기에 의하여 수신된 2차, 3차 고조파 성분은 기존 주파수 영상의 왜곡을 초래한다. 중심주파수 50 MHz, 차단주파수 20 MHz, 80 MHz로 대역폭 60 MHz를 가지는 디지털 33-탭 대역통과필터를 구현하였다. 또한 40 dB 감쇠가 일어나는 주파수를 8.1 MHz, 91.6 MHz로 설계하여 DC와 저주파수 잡음 및 고주파수 신호를 억제하였다. 설계한 대역통과필터는 FPGA의 로직 사용량을 최소화할 수 있도록 33개의 필터 계수를 대칭이 되도록 하여 Eq. (1)과 같이 절반의 필터 계수만을 사용하여 설계하였다.[8]

(1)

(1)

이때 yi는 설계한 대역통과필터의 출력 신호이고, xi는 입력 신호, hi는 필터의 계수이다. 필터 계수를 33개에서 17개로 줄임으로써 필터 구현을 위한 FPGA의 로직과 메모리 크기를 약 50 % 감소시켰다.

2.2 디지털 시간-이득 보상 블록

초음파 신호는 신체 조직을 통과할 때 산란과 흡수 등에 의하여 침투 깊이에 따라 지수 함수적으로 감소하므로 D-TGC를 통하여 주파수와 침투 깊이에 따른 감쇠를 보상하였다.[9] D-TGC 설계에서 영상 깊이는 5개의 부분 구역으로 나뉘었고, 전체 영상 깊이에 대한 개별적 선형 이득 증가 및 전체 선형 이득의 선택을 하여 제공하였다.

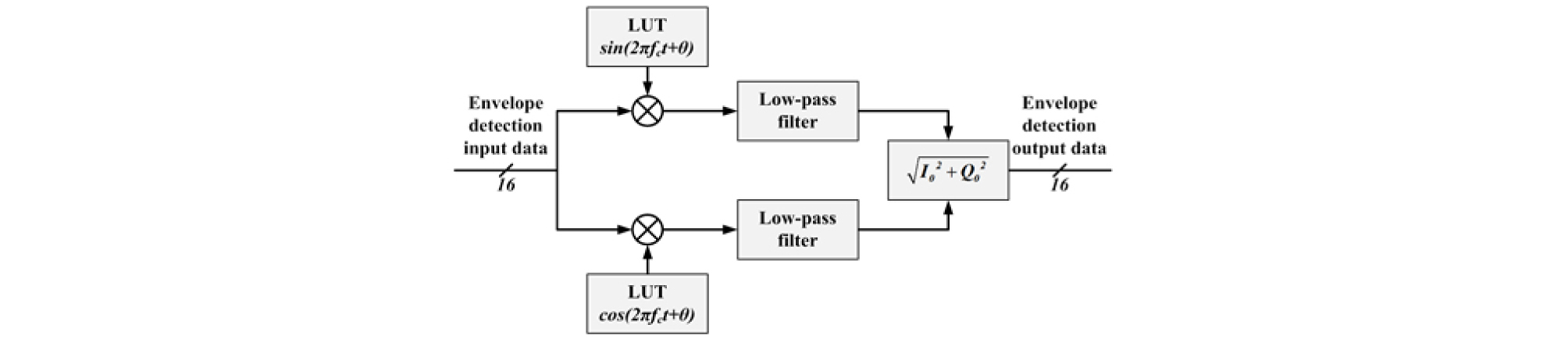

2.3 포락선 검출 블록

포락선 검출은 Fig. 2와 같은 직교복조(quadrature demodulation) 구조를 사용하였다. 연산처리속도와 로직 사용량을 줄이기 위하여 직교복조에서 동위상(I0) 성분과 직교위상(Q0) 성분 추출을 위한 중심주파수 삼각함수 파형을 LUT에 구현하여 직교복조에 필요한 연산처리 시간을 단축하였다. 포락선 검출에 사용한 저역통과필터는 차단주파수를 25 MHz, 40 dB 감쇠가 일어나는 주파수를 36.9 MHz로 설계하여 다운 샘플링 시 발생할 수 있는 엘이어싱 현상을 함께 대비하였다. 또한 저역통과필터는 FPGA의 로직과 메모리 사용량을 최소화하기 위하여 2.1절의 대역통과필터의 설계 방법과 같은 방법을 사용하여 설계하였다.

2.4 신호 선별 블록

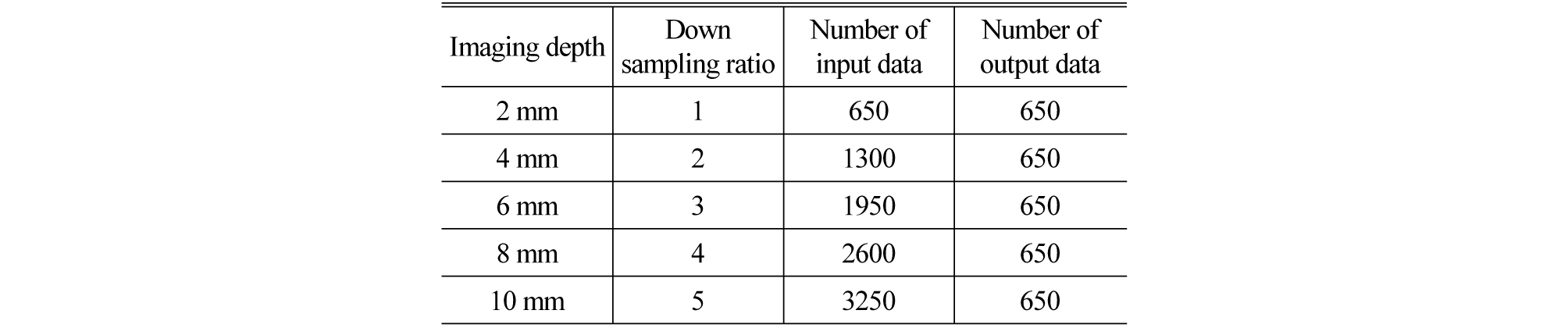

신호선별 모듈은 디스플레이 되는 혈관내초음파 영상 깊이에 맞추어 포락선 검출 신호를 선별 채택하는 역할을 한다. GUI(Graphical User Interface)상에서 줌 인, 줌 아웃 기능이 가능하도록 디스플레이 되는 영상 깊이에 맞추어 다섯 단계로 다운 샘플링 비율을 조정하여 원하는 포락선 검출 데이터만 로그압축 블록으로 전달한다. 다운 샘플링 비율은 Table 1과 같이 GUI 상의 디스플레이 되는 영상 깊이에 따라 가변적이다.

Table 1. The down-sampling ratio according to the image depth and the number of samples of input/output data. |

|

2.5 로그압축 블록

로그압축은 GUI 상에서 동적범위(dynamic range)와 로그압축 최대값을 제어할 수 있도록 Eq. (2)와 같은 로그압축 알고리즘을 사용하였다.

(2)

(2)

이때 x는 입력 데이터이고 DR은 동적 범위이며, X는 GUI에서 제어할 수 있는 로그 압축의 최대값을 나타낸다. 로그압축 알고리즘에서 로그 연산을 하는데 많은 연산처리시간과 로직 사용량이 필요하므로FPGA 로직 사용량과 연산처리시간을 줄이기 위하여 16 bit의 입력 신호에 대한 로그 연산값을 LUT로 구현하였다. 로그 연산용 LUT는 로그압축 블록의 입력 신호를 LUT의 어드레스로 적용하여 해당 어드레스의 데이터 값을 출력하는 구조로 로그 연산에 소요되는 연산처리시간을 단축하는 역할을 한다. 또한 Eq. (2)의 나누기 연산은 1/DR값을 가지는 LUT로 구현하여 GUI에서 입력되는 DR 값에 맞추어 해당 데이터값을 출력하는 방법으로 대체하여 연산처리시간을 단축하였다.

2.6 디지털주사변환 블록(Digital Scan Conversion; DSC)

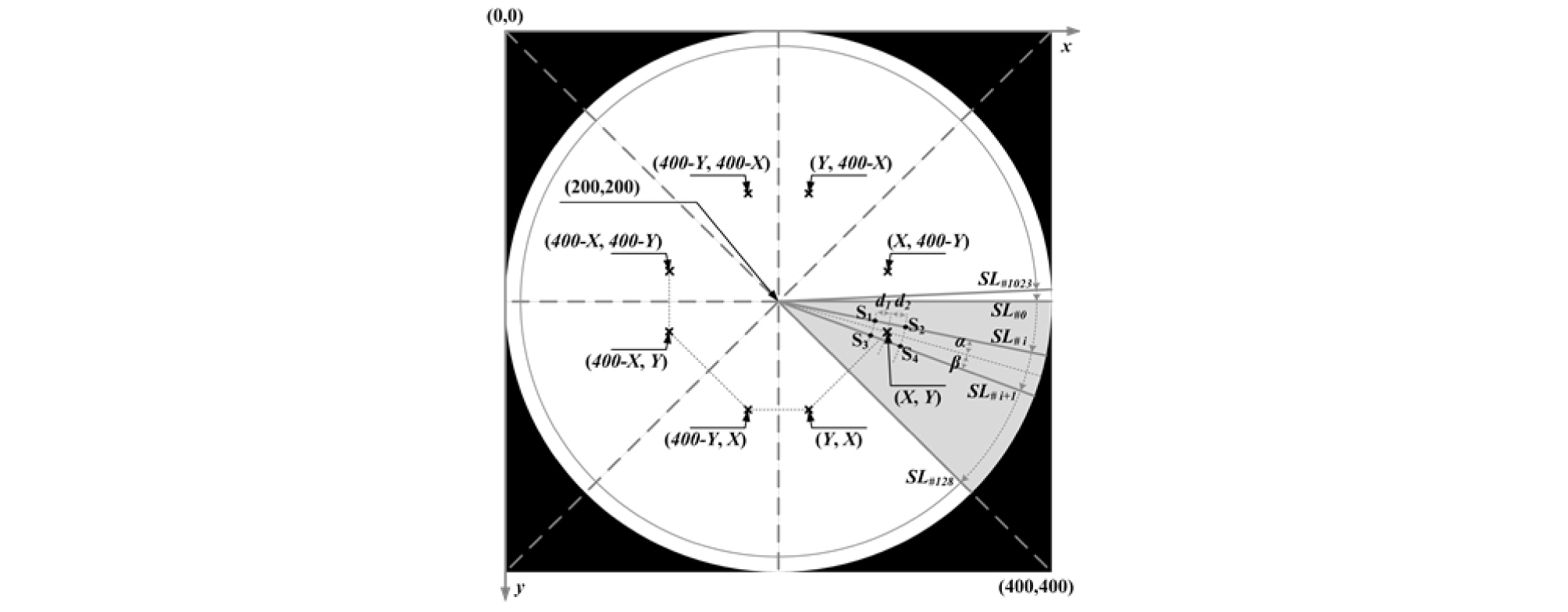

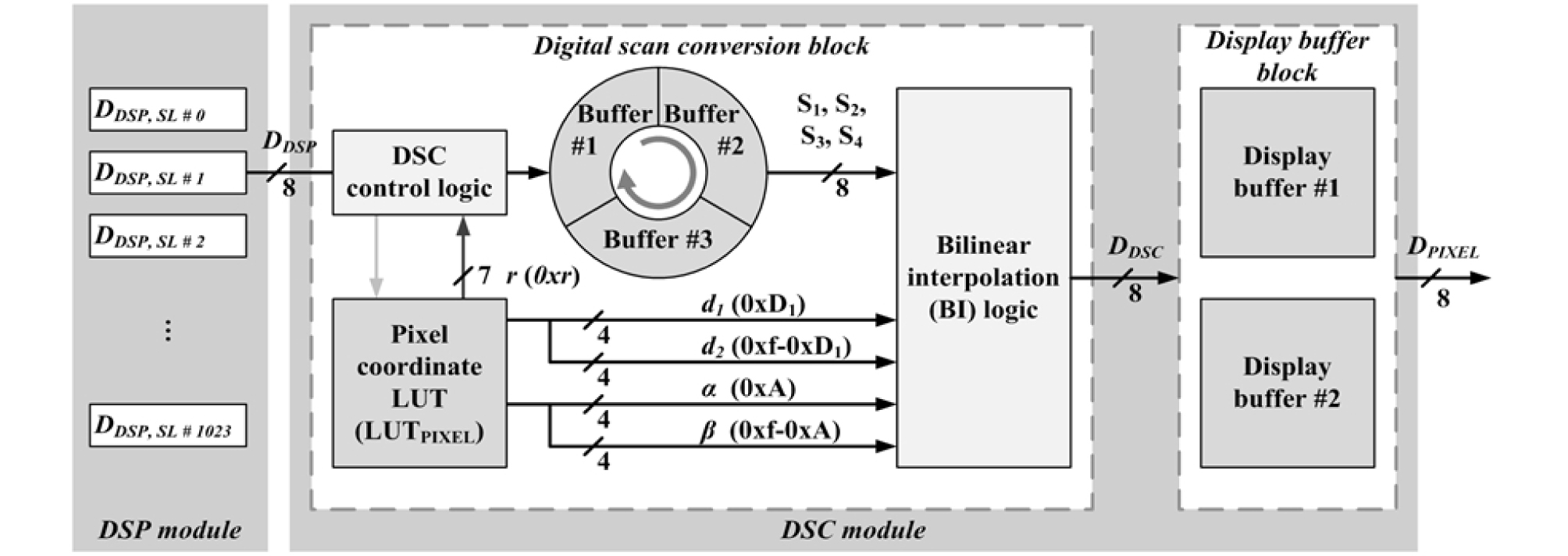

제안한 DSC 구조를 적용한 혈관내초음파 영상은 401 × 401 픽셀의 크기로 Fig. 3과 같이 대칭되는 여덟 개의 부분 영상으로 분리된다. 하나의 프레임을 구성하는 주사선을 8의 배수(8 × 128 = 1,024개)로 설정하면 하나의 부분 영상 영역(Fig. 3의 음영 영역)은 그 배수(128개)의 주사선으로 구성된다. 또한 이웃하는 두 개의 주사선을 이용하여 이중 선형 보간 기법(bilinear interpolation)으로 두 개의 주사선 사이에 위치하는 픽셀들의 데이터를 산출하는 방법을 반복하여 Fig. X의 음영 영역의 모든 픽셀 데이터를 산출 할 수 있다.[10] 제안하는 DSC 모듈은 Fig. 4와 같은 구조를 가지고 다음과 같이 동작한다. DSP된 주사선 데이터는 DSC 제어 로직을 거쳐 세 개의 버퍼에 순차적으로 저장되고 먼저 저장된 두 개의 주사선의 정보를 픽셀 정보가 저장된 LUT(LUTPIXEL)로 전송한다. LUTPIXEL에서는 두 개의 주사선을 이용하여 산출할 수 있는 모든 픽셀들의 정보[S1의 위치 정보(r, 7 bit), 샘플 사이의 거리 비율(d1, 4 bit), 주사선 사이의 각도 비율(α, 4-bit)]를 DSC 제어 로직과 BI 로직으로 픽셀 순으로 순차적으로 리턴하고 DSC 제어 로직은 주사선 데이터가 저장된 버퍼에서 해당 샘플들(S1, S2, S3, S4)의 데이터를 BI 로직으로 전달하여 각각의 픽셀 데이터를 연산 처리한다.

일반적인 DSC 구조를 사용하는 경우, 하나의 프레임을 구성하는 1,024개의 DSP된 주사선 데이터(주사선 당 8 bit 크기의 651개 샘플로 구성)를 저장하려면 메모리 용량은 5.3 M bits(8 × 651 × 1,024)가 필요하고, 디지털주사변환을 위한 메모리 용량은 적어도 1.3 M bits (401 × 401 × 8) 이상 필요하므로 최소한 6.6 M bits 이상의 메모리가 필요하다. 반면에 제안하는 DSC 구조를 적용하는 경우, 이웃하는 세 개의 주사선을 저장할 수 있는 메모리 용량인 15.6 K bits(8 × 651 × 3)와 Fig. 3의 음영 영역을 위한 메모리 용량인 322 K bits(401 × 401 × 16 ÷ 8)로 총 메모리 사용량은 337 K bits로 일반적인 DSC 구조(6.6 M bits)와 비교하여 메모리 사용량을 95 % 줄일 수 있다.

2.7 디스플레이 버퍼 블록

디스플레이 블록은 Fig. 4와 같이 두 개의 버퍼를 사용하여 버퍼 당 4,096개의 DSC된 픽셀 데이터를 저장하고 지정한 개수가 저장되면 다른 버퍼로 스왑하여 연속적으로 저장함과 동시에 기존의 버퍼에 저장되어 있던 픽셀 데이터를 호스트로 전송하는 방식으로 실시간 영상을 구현한다.

III. 후단부 시스템 성능 평가 결과 및 고찰

개발한 후단부 시스템은 74,637개의 로직 셀, 46,648개의 LUT, 132개의 DSP slice와 3,096 Kbits의 내부 메모리 용량을 가지고 있는 FPGA(XC6SLX75, Xilinx Inc., San Jose, CA)를 사용하여 구현하였다. FPGA 내부에 VHDL(VHSIC Hardware Description Language)로 구현한 후단부 시스템을 MATLAB 프로그램을 사용하여 VHDL과 동일하게 구현하여 검증하고 구현한 후단부 시스템의 FPGA 리소스 사용량을 참고문헌의 연구 결과들과 비교하였다. Ex-vivo 실험을 통하여 개발한 후단부 시스템의 실시간 혈관내초음파 영상 구현을 확인하였다.

3.1 MATLAB을 사용한 후단부 시스템 검증

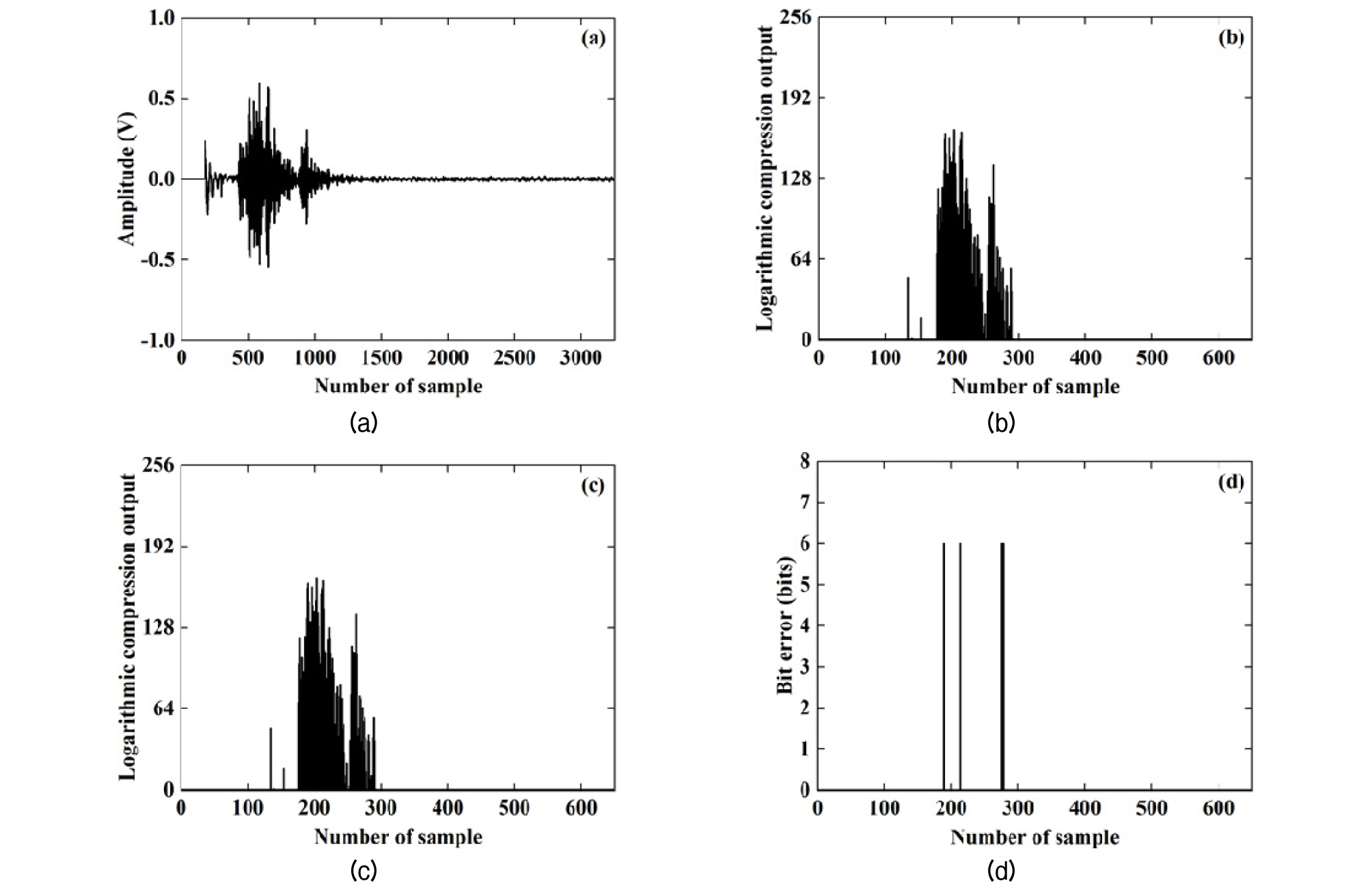

설계한 후단부 시스템을 검증하기 위하여 FPGA 내부에 VHDL로 구현한 알고리즘을 MATLAB 프로그램(Mathworks Inc., Natick, MA)을 이용하여 VHDL과 동일하게 구현하였다. Fig. 5는 설계한 VHDL 알고리즘과 MATLAB 연산을 비교한 것이다. 하나의 프레임을 구성하는 모든 주사선의 데이터 샘플을 FPGA 내부 메모리에 저장할 수 없기 때문에 시스템 검증을 위하여 추출한 주사선 데이터를 사용하였고 다운 샘플링 비율은 3인 경우의 디지털 신호 처리 출력인 로그 압축 데이터를 비교하여 설계한 VHDL 알고리즘을 검증하였다. Fig. 5. (a)는 시스템 검증을 위하여 사용한 RF 데이터이고, Fig. 5. (b)는 Chip-scope를 사용하여 저장한 FPGA의 로그 압축 데이터를 도시한 것이고, Fig. 5. (c)는 MATLAB 프로그램을 사용하여 계산한 로그 압축 데이터이고, Fig. 5. (d)는FPGA와 MATLAB을 사용하여 구현한 로그 압축 데이터 사이의 비트 에러값을 도시한 것이다. 650 샘플 중 4개의 샘플에서 6-bit의 에러가 발생한 것을 확인하였다. 1 % 이내의 에러율을 보이는 것으로 설계한 후단부 시스템의 동작 정확성을 검증하였다.

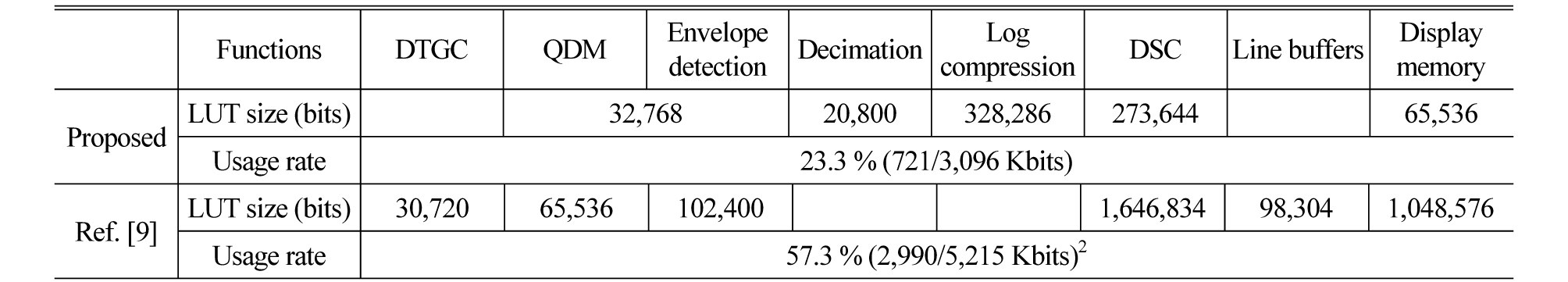

3.2 후단부 시스템 리소스 사용량 평가

Table 2는 구현한 후단부 시스템의 기능성 블록들에서 사용한 LUT 크기를 J. H. Chang et al.[11]의 연구결과와 비교하였다. 구현한 후단부 시스템이 혈관내초음파 영상 구현에 적합한 형태의 신호처리, 영상처리 구조를 가져서 QDM, DSC, 디스플레이 기억 장치 블록에서 LUT 사용량이 월등히 작은 것을 확인할 수 있다. 또한 외부 메모리를 사용하여 혈관내초음파 영상 시스템을 개발한 W. Qiu et al.[7]의 연구결과와 비교하면 구현한 후단부 시스템은 메모리 사용량을 제외하고 DSP 블록과 LUT의 사용량에 대하여 리소스의 사용이 적은 것을 확인할 수 있다.

3.3 후단부 시스템 실시간 영상 성능 평가

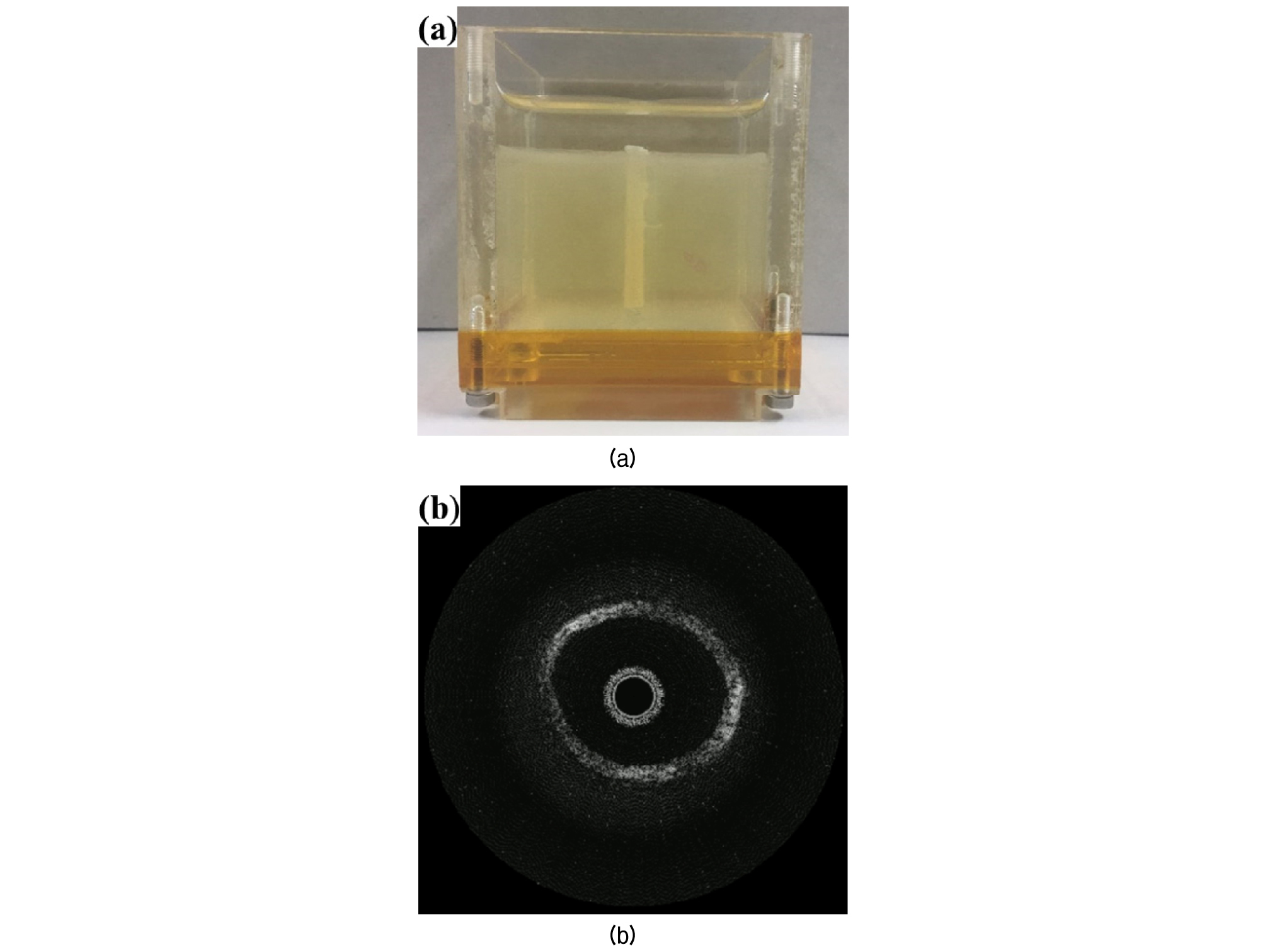

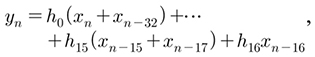

Fig. 6은 구현한 후단부 시스템의 실시간 영상 성능 평가를 위한 ex-vivo 실험에 사용한 토끼 혈관을 매립한 아크릴아마이드 생체조직모사팬텀과 실시간 혈관내초음파 영상이다. 본 실험을 위해 개발한 혈관내초음파 변환기를 사용하였으며, 정확한 사양은 발표한 논문에서 확인할 수 있다.[12] 획득한 영상의 실험 환경은 2,000 r/min의 속도로 모터를 회전시키고 한 프레임 당 1,024개의 주사선을 사용하여 혈관내초음파 영상을 구성하였고 이 때 프레임율은 초당 33.3 프레임이다. 획득한 영상은 20 MHz ~ 80 MHz 대역폭을 가지는 대역통과 필터를 적용하고 직교복조에 60 MHz의 중심주파수를 사용하였다. 선명한 영상을 위하여 D-TGC를 사용하여 토끼 혈관 영역의 이득을 높이고 주위 팬텀 영역의 이득을 줄여 혈관 영상이 뚜렷하게 하였다. 또한 6 mm의 영상 깊이의 이미지를 구현하기 위하여 신호 선별 블록에서 다운샘플링 비율을 3으로 설정하고 로그 압축에 사용되는 파라미터, 로그압축 최대값은 70 dB, 동적범위는 40 dB로 설정하여 실시간 혈관내초음파 영상을 획득하였다. 토끼 혈관을 이용한 ex-vivo 실험을 통하여 개발한 후단부 시스템이 실시간 혈관내초음파 영상을 구현함에 적합함을 확인하였다.

3.4 고찰

구현한 후단부 시스템은 LUT을 이용하여 FPGA 내부 로직 사용량과 연산처리시간을 대폭 줄였고 혈관내초음파 영상에 최적화된 DSC 구조를 사용하여 메모리 사용량을 최소화하면서 실시간 영상 구현이 가능한 것을 확인하였다. 이를 바탕으로 적용 분야에 맞추어 DSC 모듈 구조를 변경하면 외부 메모리 없이 단일 FPGA의 내부 메모리만으로 데이터 용량이 많은 고주파수, 고해상도의 초음파 영상 시스템에 적용할 수 있을 것이라 판단된다.

IV. 결 론

본 논문은 혈관내초음파 영상에 특화된 후단부 시스템의 설계 및 성능평가 결과에 대하여 설명하였다. 개발한 후단부 시스템은 실시간 혈관내초음파 영상의 구현이 가능하도록 연산처리시간이 긴 연산들을 LUT로 대체하여 연산처리시간을 단축하고 새로운 DSC 알고리즘을 적용하여 적은 메모리를 사용하는 구조를 사용하였다. 개발한 후단부 시스템의 알고리즘을 MATLAB으로 동일하게 구현하여 시스템 알고리즘을 검증하였고 토끼 혈관을 이용한 ex-vivo 실험을 통하여 개발한 후단부 시스템이 실시간 혈관내초음파 영상의 구현함에 적합함을 확인하였다. 즉, 외부 메모리 없이 단일 FPGA만으로 고주파수, 고해상도의 실시간 영상 구현이 가능함을 확인하였다. 제안한 후단부 시스템 알고리즘을 적용하면 고주파수, 고해상도 초음파 영상 처리 시스템의 저비용, 소형화, 경량화가 가능할 것이다.