I. 서 론

II. 정합 회로와 역률 개선 튜닝 회로

III. 두 개의 공진점을 갖는 광대역 전기 음향 변화기의 역률 개선을 위한 등가 모델

IV. 체비셰프 회로 설계법과 추가 최적화를 이용한 역률 개선 회로 설계법

4.1 체비셰프 회로 설계법에 의한 역률 개선 회로 설계

4.2 역률 개선 가능성 척도 및 회로 보정

4.3 사후 최적화를 이용한 회로 개선

V. 모의 실험

VI. 결 론

I. 서 론

정합 방법이 많이 연구되어 있지만 광대역 정합법은 여전히 관심의 대상이 되고 있다. 이는 광대역 정합을 하기 위해서는 부하가 주파수의 함수가 되는 것을 감안하여야 하기 때문이다. 광대역 정합법으로 Fano의 정합법뿐만 아니라 실 주파수 정합법(real frequency matching technique) 등 여러 유명한 접근법이 있다.[1-5] 이와 같은 정합은 파워 앰프 내부 저항과 부하 저항 사이에 파워를 잘 전달하고자 하는 시도이다. 그러나 파워 앰프의 내부저항이 매우 작은 경우 정합 회로를 구성하기 보다는 부하 측의 역률을 개선하는 것을 선호 한다.[6] 기존 연구의 결과를 살펴 보면 광대역에서 최대 파워를 전달하게 하는 정합회로를 구하는 방법을 많이 연구되어 왔으나,[7,8] 두 개의 공진점을 갖는 광대역 전기 음향 변화기에 적용할 만한 광대역 역률 개선용 튜닝 회로를 구성하는 방법은 저자의 조사에 의하면 거의 발견할 수 없다.

본 논문에서는 공진점간 상호 결합이 적은 두 개의 공진점을 갖는 광대역 전기 음향 변화기의 역률 개선을 위한 회로 설계법을 제안한다. 본 설계법은 기존에 단공진 변환기에 많이 쓰이던 체비셰프 설계법을 두 개의 공진이 있는 변환기에도 쓸 수 있도록 하였고, 이를 다시 최적화 함으로써 좀 더 좋은 특성의 회로를 얻도록 하였다. 부수적으로 대상 트랜스듀서를 원하는 만큼 역률 개선할 수 있는지 평가할 수 있는 척도도 구해져서, 객관적인 역률 개선을 할 수 있게 되었다.

II. 정합 회로와 역률 개선 튜닝 회로

정합회로가 전원으로부터 부하로 최대의 파워를 전달하려면, 아래와 같은 조건이 만족 되어야 한다.

조건1: Xs와 XL은 서로 상쇄된다. 즉 Xs=-XL.

조건2: Rs=RL

위 그림과 같이 관점을 입력으로 맞춰 Zin을 생각하면, Zin=Zs*이다. 이때 Zs가 순수 저항이라면, Zin도 실수 값만 가져야 함을 알 수 있다. 이를 바탕으로 생각하면 정합회로는 부하의 허수 항을 소거하는 역할을 하고 있음을 알 수 있다.

다음 그림은 역율에 관한 정의를 나타내는 그림이다.

역률은 소스에서 부하로 전달하는 전체 파워 중에서 실수 성분의 비율을 의미한다. 따라서 역률을 개선한다는 것은 위 그림의 각을 ‘0’에 가깝게 만든다는 것이고, 이를 그림 2를 이용하면 다시 쓰면, Zin에서 실수 부분보다 허수 부분을 작게 해야 한다는 것이다. 이상적으로는 허수 부분을 ‘0’으로 만들어야 한다. 위의 정합회로와 역률에 대한 기술을 종합하면, 정합회로 사용하면 역율 개선을 할 수 있는 가능성이 있음을 알 수 있다. 다만 그 회로가 최적이 회로가 된다는 보장을 없으나, 최적 회로를 구하는 좋은 초기 조건 역할을 하는 회로 구성은 가능함을 알 수 있다.

|

그림 1.일반적인 정합회로 Fig. 1.Power matching circuit. |

|

그림 2.역율의 정의 Fig. 2.Definition of the power factor. |

III. 두 개의 공진점을 갖는 광대역 전기 음향 변화기의 역률 개선을 위한 등가 모델

다음 그림은 두 개의 공진점을 갖는 전기 음향 변환기의 등가 회로이다. 이와 같이 서로 다른 대역을 갖는 두 개의 부하를 단일한 회로를 사용하여 정합 회로를 설계하는 해석적인 방법은 발표된 연구 결과를 찾기 힘들다.

|

그림 3.두 개의 공진점을 갖는 전기 음향 변환기의 등가 회로 Fig. 3.Equivalent circuit for an electro acoustic transducer with dual resonance. |

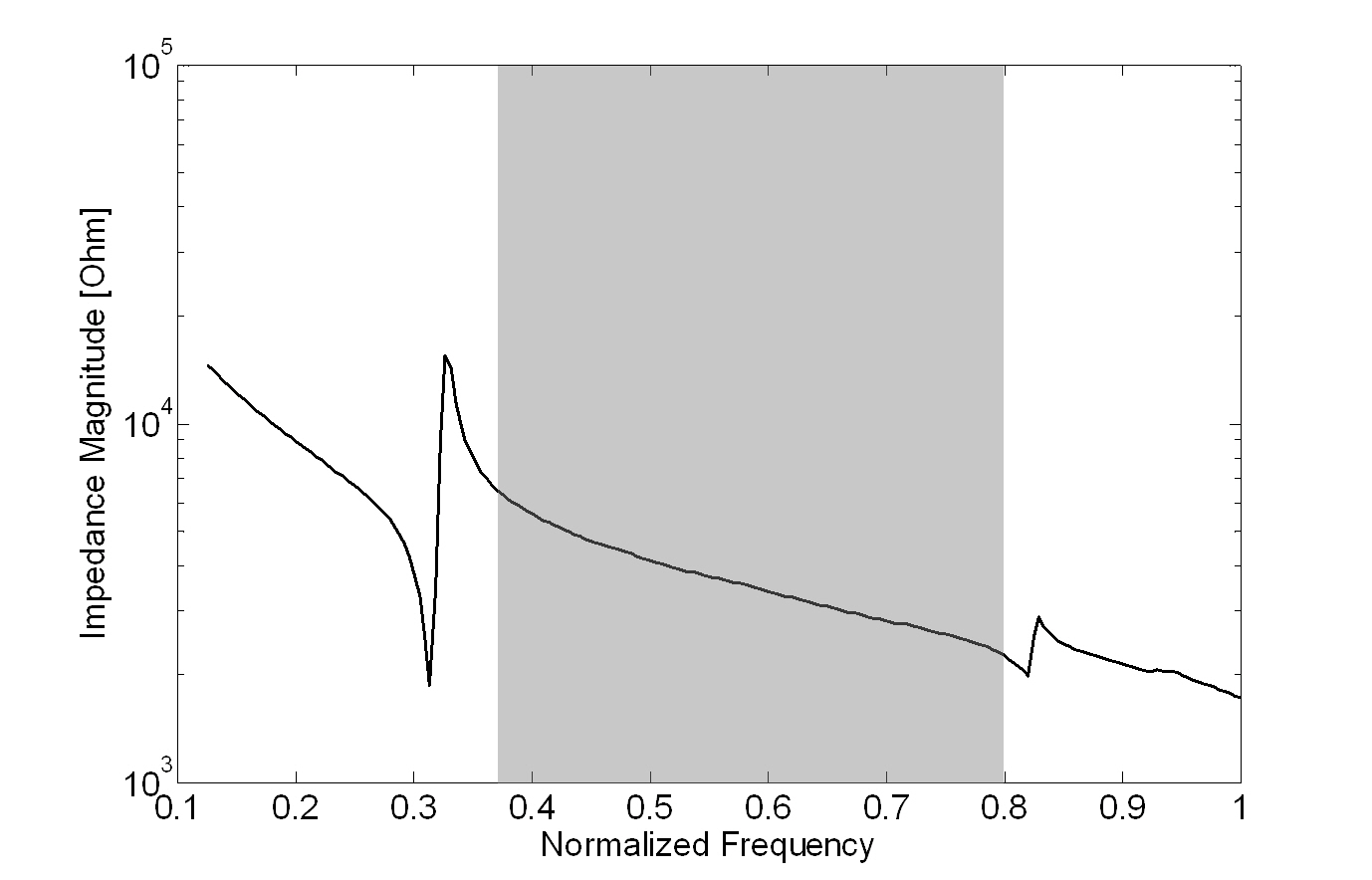

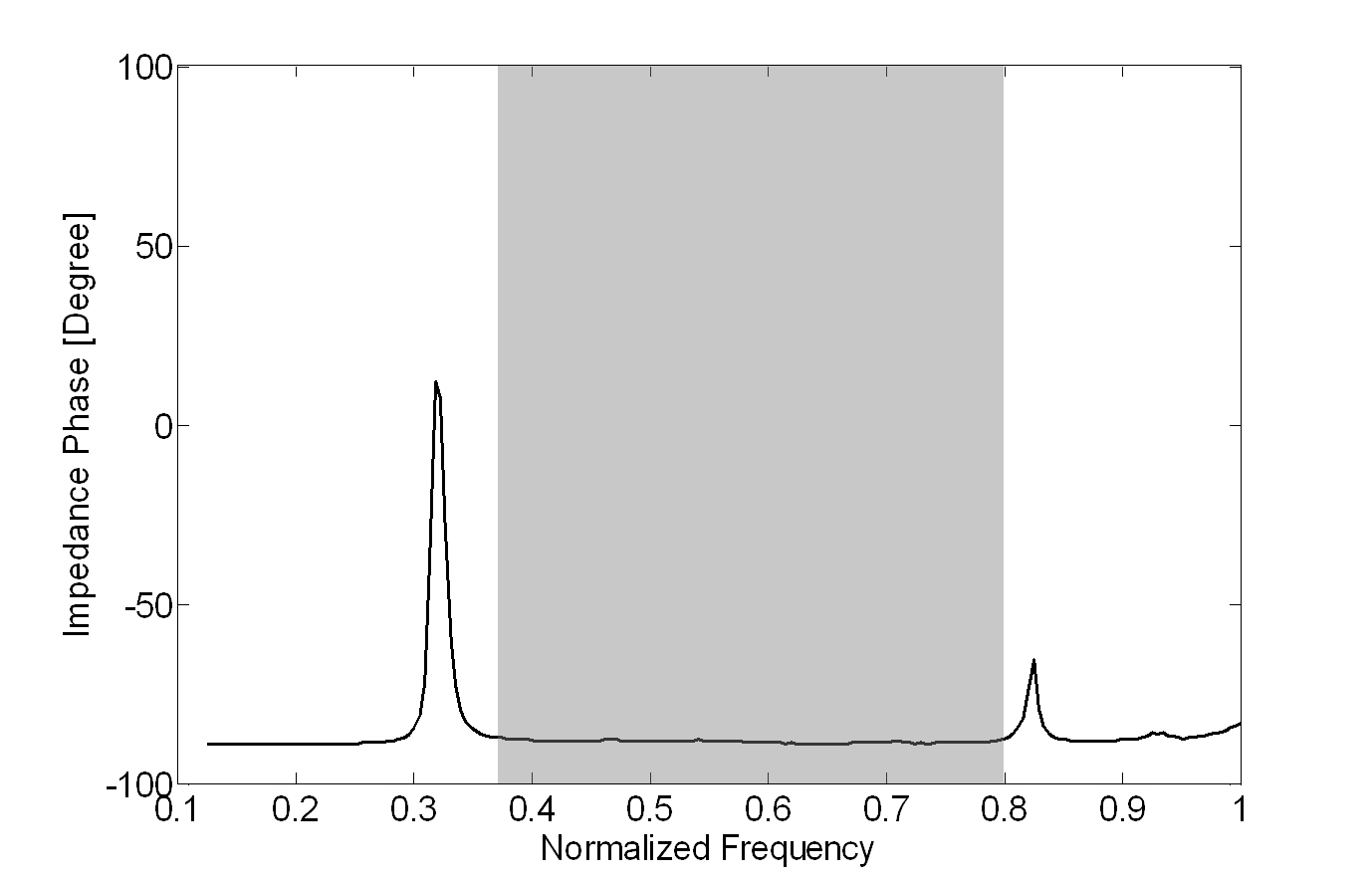

그러나 광대역을 만들려고 공진점간 거리를 많이 떨어뜨려서 두 공진점 간의 상호 결합이 적은 경우, 아래 그림과 같이 두 공진점 사이의 주파수대에 주목하면, 임피던스의 위상이 거의 90도에 이르고 크기는 주파수가 높아지면서 점점 줄어드는 경향을 보인다. 이를 보면 관점을 두 공진점을 포함한 전 대역폭보다 공진점 사이의 주파수대를 주된 목표로 광대역화를 하려 한다면 등가회로가 다음 그림 5와 같이 단순해지고, 이런 단순한 부하는 고전적인 해석적 방법으로 회로를 구할 수 있다.

아래 임피던스 그림 4에서 그림자로 표시된 부분을 관심 대역으로 하여 새로운 등가 회로를 구하면 그림 5와 같은 단순한 등가회로가 된다.

IV. 체비셰프 회로 설계법과 추가 최적화를 이용한 역률 개선 회로 설계법

4.1 체비셰프 회로 설계법에 의한 역률 개선 회로 설계

3장에서 파워 정합을 사용하면 어느 정도 역률 개선 효과를 얻을 수 있다는 가능성을 살펴 보았다. 따라서 본 절에서는 일반적으로 파워 정합회로 설계에서 많이 사용하고 있는 체비셰프 설계법을 기반으로 한 설계 법을 그림 5와 같은 부하에 대해서 정합회로를 구하는 것을 살펴 본다. 아래 식(1)은 n 차의 주파수축 이득 함수이다. 그리고 이 식의 분모 중 Tn( )는 체비셰프 함수를 이용하고 있다.

| (1) |

여기서 Tn( )는 다음과 같이 정의된다.

![]() , 이고

, 이고 ![]() 이다. 식(1)에서, M은 이득 값이고, 범위는 0 < M < 1 이다. τ 는 양수로 된 맥동 조절 값이다. ωc는

이다. 식(1)에서, M은 이득 값이고, 범위는 0 < M < 1 이다. τ 는 양수로 된 맥동 조절 값이다. ωc는 ![]() 가 1의 값을 갖는 최대 주파수로써 컷오프 주파수가 된다. 이를 체비셰프 이득함수라고 한다. 필터 합성할 때, M은 ‘1’이여야 하지만, 파워 정합 회로나 본 논문과 같은 광대역 튜닝 회로를 만들 때는 M값이 ‘1’보다 작은 경우로 설정하는 것도 가능하다. 위 (1)의 이득 함수로부터 L-C 4단자망을 구성하기 위해서는 아래와 같은 관계식을 이용한다.

가 1의 값을 갖는 최대 주파수로써 컷오프 주파수가 된다. 이를 체비셰프 이득함수라고 한다. 필터 합성할 때, M은 ‘1’이여야 하지만, 파워 정합 회로나 본 논문과 같은 광대역 튜닝 회로를 만들 때는 M값이 ‘1’보다 작은 경우로 설정하는 것도 가능하다. 위 (1)의 이득 함수로부터 L-C 4단자망을 구성하기 위해서는 아래와 같은 관계식을 이용한다.

| (2) |

다음으로는 ρ(s)으로부터 부하의 저항에서 소스 쪽을 들여다본 임피던스 식을 구한다.

| (3) |

위에서 구한 임피던스 Z(s)는 L-C 사다리형 회로 합성 방법을 이용하여 구체적인 회로로 구성할 수 있다.[9] 위 방법은 보통 단순 저항만이 부하일 때를 적용 가능하지만, 그 외의 특정한 부하 조건에서도 체비셰프 이득함수를 바탕으로 최적화하는 방법이 개발되어 있다. 이 특정한 부하 조건 중에는 저항과 캐패시터가 병렬로 연결된 경우도 포함된다.[1,10] 저항과 캐패시터가 병렬로 연결된 경우는 앞 장에서 살펴본 바와 같이 본 논문에서 관심이 있는 두 개의 공진점이 있는 전기 음향 변환기의 공진점 사이의 임피던스 특성과 매우 유사하다. 따라서 기존의 개발된 방법론을 이용할 수 있다.

RC병렬 연결된 부하에 대해서 튜닝 필터용 소자를 구하기 위해서 앞서 설명한 방법을 사용할 수도 있지만, Weinberg 관계식이라고 불리는 식을 사용하여 설계 사양으로부터 직접적으로 소자를 구할 수 있다. 다음은 부하의 소자값으로부터 시작하여 Weinberg 관계식을 사용해서 소자값 구하는 순차식이다.[1,10]

| (4) |

| (5) |

| (6) |

여기서 R1과 C1은 각각 부하를 이루는 소자값이다. 또 위 식에서 필요한 a, b는 다음과 같다.

| (7) |

또 sk와 bk는 다음과 같은 관계식에서 구한다.

| (8) |

| (9) |

4.2 역률 개선 가능성 척도 및 회로 보정

4.1절에 식(1)의 최종 가용 이득은 근사식 ![]() 로 표현할 수 있다.[1] 여기서 RnCn은 정규화된 저항과 캐패시터의 곱이다. 이 곱을 ωc로 비정규화된 것으로 바꾸면 RCωc가 된다. 본 논문에서는 R값을 트랜스듀서의 임피던스 값으로부터 직접 구해서 쓰므로 Rn=R인 관계가 성립되어 Rn은 비정규화 할 필요가 없다. 비정규화 과정을 거치면,

로 표현할 수 있다.[1] 여기서 RnCn은 정규화된 저항과 캐패시터의 곱이다. 이 곱을 ωc로 비정규화된 것으로 바꾸면 RCωc가 된다. 본 논문에서는 R값을 트랜스듀서의 임피던스 값으로부터 직접 구해서 쓰므로 Rn=R인 관계가 성립되어 Rn은 비정규화 할 필요가 없다. 비정규화 과정을 거치면, ![]() 을 얻을 수 있다. 이 식으로부터 새로운 관계를 얻을 수 있다. 즉 가용 이득이 1에 근접하려면, RCωc에 상한값이 존재한다는 것이다. 다시 말해서 기존 전기 음향 변환기의 부하의 등가회로를 구하고, 그 등가회로의 저항과 캐패시터 및 최대 주파수를 곱한 값과

을 얻을 수 있다. 이 식으로부터 새로운 관계를 얻을 수 있다. 즉 가용 이득이 1에 근접하려면, RCωc에 상한값이 존재한다는 것이다. 다시 말해서 기존 전기 음향 변환기의 부하의 등가회로를 구하고, 그 등가회로의 저항과 캐패시터 및 최대 주파수를 곱한 값과 ![]() 로부터 예상하는 이득을 구할 수 있다. 앞에서 기술한 바와 같이 정합회로가 잘 정합되었을 때의 이득은 역률을 반영하는 경향이 있으므로 원하는 역률을 얻을 수 있는지 여부도 알 수 있다. 만약 예상 이득이 매우 작다면, 원하는 역률을 얻을 수 없다는 것을 의미 하므로 RCωc을 더 작게 만들 필요가 생긴다. 즉 트랜스듀서 외부에 역률 개선 회로 외에 추가로, 트랜스듀서의 특성을 바꾸는 보정 소자를 달아야 한다는 의미가 된다. 반면에 예상 이득이 ‘1’에 가깝다면, 역률도 좋을 것이 예상되어 외부에 트랜스듀서 외부에 특성을 바꾸는 보정 소자가 없이도 됨을 의미한다. 다시 말해서 기존 전기 음향 변환기의 공진점과 공진점 사이의 임피던스 데이터로부터 R과 C의 병렬 등가회로를 구하면, RCωc 값으로부터 그 전기 음향 변환기를 순수하게 체비셰프 방법만으로 1에 가까운 이득 또는 역률을 얻을 수 있는지 또는 외부에 트랜스듀서 특성 보정용 소자를 덧붙인 후에 체비셰프 방법으로 이득 또는 역률 개선을 할 수 있는지를 판단할 수 있는 근거가 될 수 있다.

로부터 예상하는 이득을 구할 수 있다. 앞에서 기술한 바와 같이 정합회로가 잘 정합되었을 때의 이득은 역률을 반영하는 경향이 있으므로 원하는 역률을 얻을 수 있는지 여부도 알 수 있다. 만약 예상 이득이 매우 작다면, 원하는 역률을 얻을 수 없다는 것을 의미 하므로 RCωc을 더 작게 만들 필요가 생긴다. 즉 트랜스듀서 외부에 역률 개선 회로 외에 추가로, 트랜스듀서의 특성을 바꾸는 보정 소자를 달아야 한다는 의미가 된다. 반면에 예상 이득이 ‘1’에 가깝다면, 역률도 좋을 것이 예상되어 외부에 트랜스듀서 외부에 특성을 바꾸는 보정 소자가 없이도 됨을 의미한다. 다시 말해서 기존 전기 음향 변환기의 공진점과 공진점 사이의 임피던스 데이터로부터 R과 C의 병렬 등가회로를 구하면, RCωc 값으로부터 그 전기 음향 변환기를 순수하게 체비셰프 방법만으로 1에 가까운 이득 또는 역률을 얻을 수 있는지 또는 외부에 트랜스듀서 특성 보정용 소자를 덧붙인 후에 체비셰프 방법으로 이득 또는 역률 개선을 할 수 있는지를 판단할 수 있는 근거가 될 수 있다.

만약 RCωc 곱이 너무 커서 보정용 소자를 트랜스듀서 외부에 보정해야 한다면, 이론적으로 R을 줄이는 방법과 C를 줄이는 방법 중 하나를 택할 수 있다. 그러나 실제로 회로 소자를 고려할 경우 R을 줄이는 것은 또 다른 저항을 트랜스듀서 신호선 양단에 병렬 연결하면 되나, C을 줄이는 것은 간단하지 않다. 만약 협대역 응용이라면 L을 이용하여 보정하는 것을 생각할 수 있으나, 광대역 응용을 목표로 할 때는 L소자 하나로 간단한 보정 회로를 만들 수 없고, 원하는 광대역에 걸쳐서 음의 캐패시턴스 값을 내는 회로를 따로 꾸며야 한다. 이는 또 다른 문제라서 본 논문에서는 제외하였다. 즉 보정용 소자로 저항 R을 병렬로 덧붙여서 전체 RCωc 값이 작아지도록 하였다. 그리고 위 식으로부터 적당한 상한 값도 얻을 수 있는데 RCωc의 상한을 ‘3’정도로 정하면, ![]() , 비교적 합리적인 성능의 회로를 얻을 수 있다. 그러나 성능의 우수성을 보장하려면 ‘2’미만의 값을 택해서,

, 비교적 합리적인 성능의 회로를 얻을 수 있다. 그러나 성능의 우수성을 보장하려면 ‘2’미만의 값을 택해서, ![]() , 선택하는 것이 좋다.

, 선택하는 것이 좋다.

위 표 1은 앞에서 기술한 역률 개선 가능성 척도 및 회로 보정에 관한 사항을 정리한 것이다. 이 표를 참고하여 역률 개선 회로를 설계한다면, 대상 트랜스듀서의 역률 개선할 수 있는지 여부를 판단할 수 있고, 역률을 개선한다면 어떤 형태로 개선할 수 있는지도 알 수 있다.

4.3 사후 최적화를 이용한 회로 개선

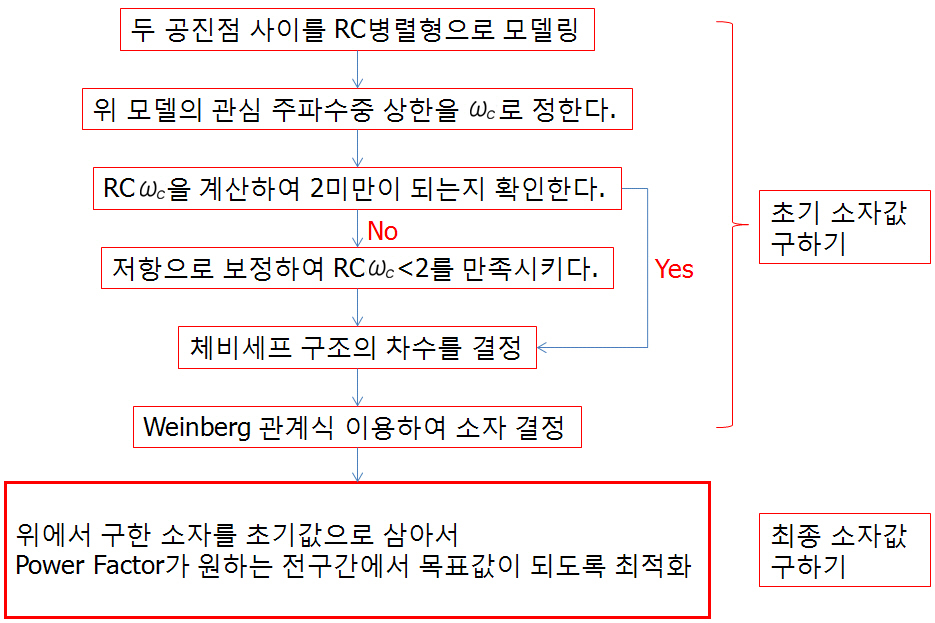

위와 같은 방법으로 통해서 튜닝 회로를 구하면 초기에 원하는 역률을 갖는 회로를 얻을 수 있다. 그러나 이 회로는 체비셰프라는 다항식에서 최적값이므로 좀 더 좋은 성능을 갖는 회로 구성을 할 수 있는 가능성이 존재 한다. 따라서 본 논문에서는 위에서 구한 체비셰프 과정으로 구한 소자값을 초기값으로 하는 또 한번의 최적화 과정을 사용한다.

즉, 추가된 제한 조건을 갖는 최소 자승법을 사용한 최적화법을 수행한다. 이때 사용하는 목적함수은 최적화된 음향 트랜스듀서에서 발생하는 TVR 수준이 원하는 값이 되어야 하고, 동시에 전체 회로의 위상은 ‘0’을 유지하여야 한다는 제한조건을 부가하였다. 이를 수식으로 나타내면, 다음과 같다.

목적함수:

| (10) |

여기서 Zin은 그림 1에 표시된 입력 임피던스이다. 4장에서 서술한 역률 개선 회로 설계방법을 흐름도로 요약 하면 그림 6과 같다.

|

그림 6.제안한 최적화법 흐름도 Fig. 6.Proposed optimization flow. |

V. 모의 실험

제안한 방법의 타당성을 보이기 위하여 본 논문에서는 참고문헌 [11]과 같은 트랜스듀서 전면부분에 공간이 있는 구조를 선택하였다. 그 이유는 이 구조의 트랜스듀서가 광대역을 얻기 위해서 공진점간 거리를 많이 띄어 놓았고 그 사이의 결합도 적은 특성을 나타내어 본 논문에서 제안한 방법에 어울리기 때문이다. 정규화된 주파수로 나타낸 트랜스듀서의 임피던스 크기와 위상은 그림 4와 같다.

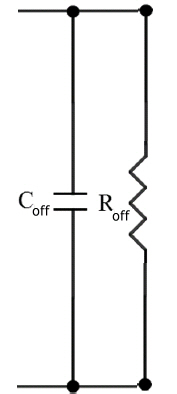

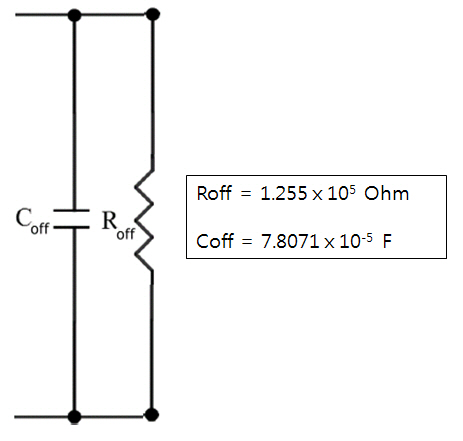

앞에서와 기술한 것과 같이 전체 회로를 대상으로 하지 않고 공진점과 공진점 사이의 대역을 주된 목표로 하기 위해서 그림 4에 그림자 표시로 된 주요 관심 대역에 대해서 등가회로를 다시 구하면 그림 7과 같은 등가회로를 구할 수 있다.

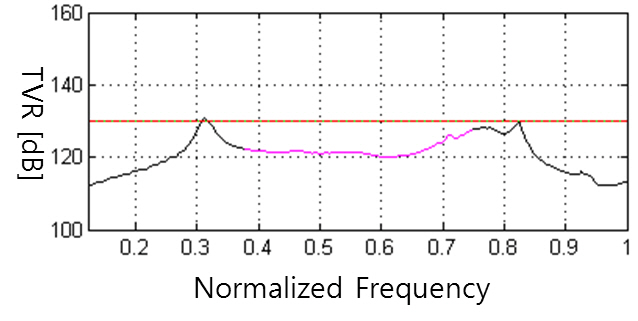

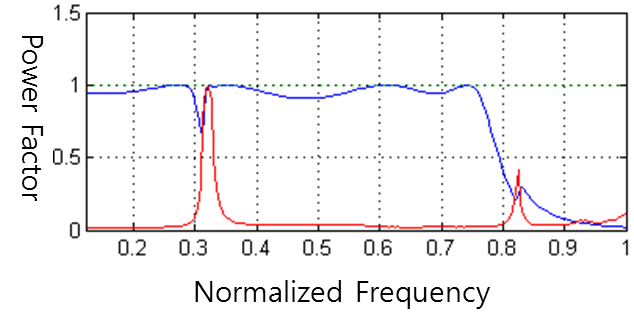

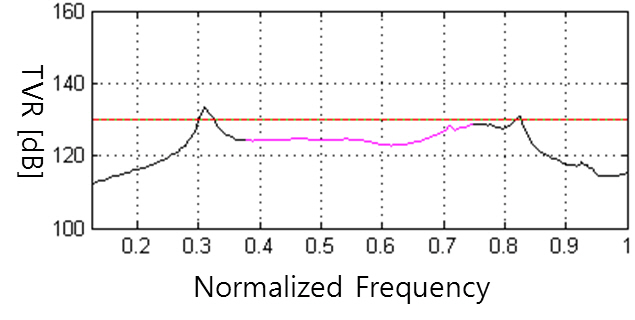

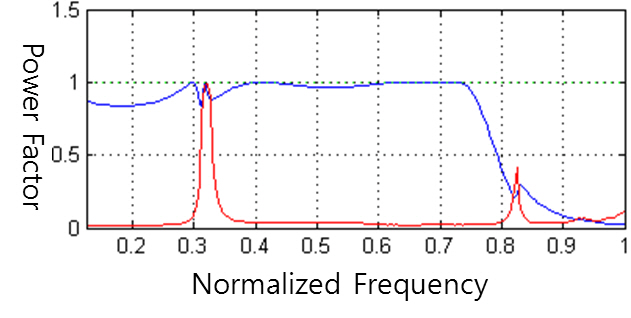

그림 7의 등가회로를 대상으로 그림 6에 제안한 복합 최적화 방법을 통해 튜닝 회로를 구성을 하였다. 위 등가 회로를 가지고 ωc를 0.75로 잡았을 때, 그림 6의 초기값 구하기 단계에서 RCωc의 값이 2 미만이 되는지 점검한 결과 표 1에 따라 보정이 필요하다는 결과가 나와서 본 실험에서는 RCωc의 값이 2 미만이 되도록 5 kΩ을 트랜스듀서 외부에 병렬로 설치하도록 하였다. 그리고 나머지 단계를 수행한 결과는 다음과 같다. 그림에서 (a)와 (b)는 체비셰프 방법으로만 구성한 회로로 얻은 일률과 TVR값이고, (c)와 (d)는 체비셰프 결과를 바탕으로 한번 더 최적화를 한 후의 일률과 TVR이다. 두 세트를 서로 비교하면, 체비셰프 방법만으로도 어느 정도 성능을 얻을 수 있으나, 한번 더 최적화를 하면 더 좋은 결과를 얻을 수 있음을 알 수 있다.

|

그림 7.실험 대상 전기 음향 소자의 공진점 사이 구간에서의 등가 회로 Fig. 7.An equivalent circuit for the impedance between two resonances in simulation transducer. |

그림 9는 제안한 최적화 방법을 사용하여 얻은 그림 8과 같은 결과를 내는 외부 회로와 트랜스듀서를 함께 그린 그림이다.